# STARTECH SEMICONDUCTOR, INC.

DATA BOOK 1991

STARTECH PRODUCT DATA BOOK 1991

|   | COMMUNICATION         |

|---|-----------------------|

| 2 | MASS STORAGE          |

| 3 | UART                  |

| 4 | UART/COMBO            |

| 5 | APPLICATION NOTES     |

| 6 | QUALITY/RELIABILITY   |

|   | ORDERING INFORMATION  |

| 8 | PACKAGING INFORMATION |

| 9 | REPRESENTATIVES       |

|   |                       |

#### **PRODUCT LIST**

| ST16C450  | Low power CMOS universal serial transmitter and receiver.                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 31100430  | Low power civics universal serial transmitter and receiver.                                                                                       |

| ST16C2450 | Low power CMOS Dual universal serial transmitter and receiver.                                                                                    |

| ST16C454  | Low power CMOS Quad universal serial transmitter and receiver.                                                                                    |

| ST16C452  | Low power CMOS Dual universal serial transmitter and receiver with parallel printer port.                                                         |

| ST16C550  | Low power CMOS universal serial transmitter and receiver with 16 byte FIFO.                                                                       |

| ST16C2550 | Low power CMOS Dual universal serial transmitter and receiver with 16 byte FIFO.                                                                  |

| ST16C554  | Low power CMOS Quad universal serial transmitter and receiver with 16 byte FIFO.                                                                  |

| ST68C554  | Low power CMOS Quad universal serial transmitter and receiver with 16 byte FIFO for Motorola, Rockwell, Hitachi and similar base microprocessors. |

| ST16C552  | Low power CMOS Dual universal serial transmitter and receiver with 16 byte FIFO and parallel bidirectional printer port.                          |

| ST84C71   | Low power CMOS 16 bit IDE interface with floppy and hard disk decode logic.                                                                       |

| ST26C31   | Low power CMOS high speed Quad RS-422, RS-423 differential line driver.                                                                           |

| ST34C87   | Low power CMOS high speed Quad RS-422, RS-423 differential line driver.                                                                           |

| ST26C32   | Low power CMOS high speed Quad RS-422, RS-423 differential line receiver.                                                                         |

| ST34C86   | Low power CMOS high speed Quad RS-422, RS-423 differential line receiver.                                                                         |

| ST86C87   | Low power CMOS high speed Dual RS-422, RS423 differential line receiver and driver.                                                               |

| ST41C76   | Low power CMOS high speed 6 bit video DAC.                                                                                                        |

|           | <u> </u>                                                                                                                                          |

No part of this document may be copied or reproduced in any form or by means without the prior written consent of STARTECH Semiconductor Inc. The information in this document is subject to change without notice. STARTECH Semiconductor Inc. assumes no responsibility for any errors that may appear in this document and makes no commitment to update or to keep current the information containd in this document. STARTECH Semiconductor Inc. makes no warranty (express, statutory, implied, or by description) regarding the information set forth herein or regarding the freedom of the described device form patent infringement. STARTECH Semiconductor Inc. makes no warranty of merchantability or fitness for any purpose.

### **CONTENTS**

| ST16C450  | 3-3   |

|-----------|-------|

| ST16C452  | 4-3   |

| ST16C454  | 3-21  |

| ST16C550  | 3-37  |

| ST16C552  | 4-27  |

| ST16C554  | 3-57  |

| ST16C2450 | 3-73  |

| ST16C2550 | 3-91  |

| ST26C31   | 1-3   |

| ST26C32   | 1-5   |

| ST34C86   | 1-7   |

| ST34C87   | 1-9   |

| ST68C554  | 3-109 |

| ST86C87   | 1-11  |

| AN-550    | 5-3   |

| AN-552    | 5-5   |

| AN-554    | 5-7   |

| AN-2550   | 5-9   |

| AN-8471   | 5-11  |

## **COMMUNICATION**

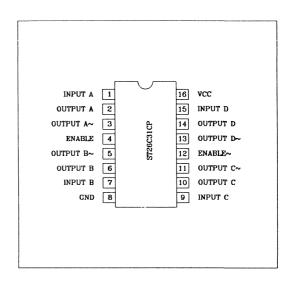

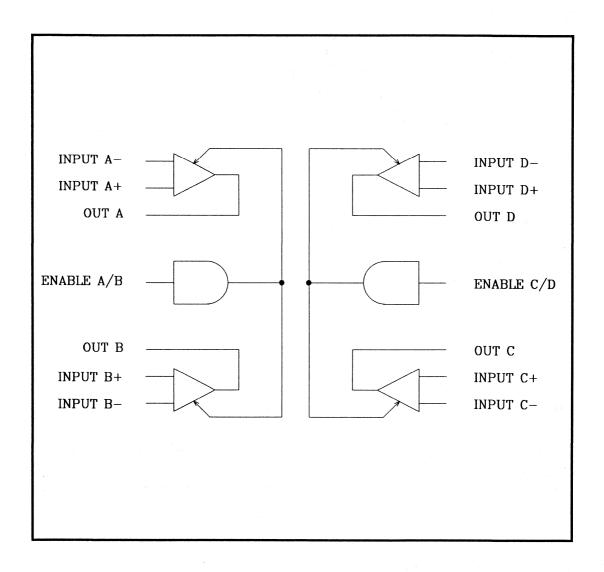

### QUAD RS-422, RS-423 CMOS DIFFERENTIAL LINE DRIVER

#### DESCRIPTION

The ST26C31 is a CMOS quad differential line driver, designed to meet the standard RS-422, RS-423 requirements and digital data transmission over balanced lines. To improve noise margin and output stability for slow changing input signal special hysteresis is built in the ST26C31 circuit.

#### **FEATURES**

- \* Pin-to-pin compatible with National DS26C31C

- \* Low power CMOS design

- \* Three-state outputs with enable pin

- \* Meets the EIA RS-422 requirements

- \* Low propagation delays

- \* High speed

#### **APPLICATIONS**

- \* Hard disk drives

- \* RS-422 controller cards

- \* MFM / RLL controller cards

- \* Digital line transmission driver

#### **GENERAL DESCRIPTION**

The ST26C31 is a high speed CMOS line driver, designed to operate with MFM / RLL controllers and hard disk drives as well as RS-422 and RS-423 digital data transmission applications. ST26C31 is suitable for low power 5V operation with high input voltage protection devices.

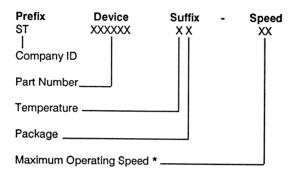

#### ORDERING INFORMATION

Part number

Package

Operating temperature

ST26C31CP16

Plastic

0° C to + 70° C

ST26C31CJ18

PLCC

0° C to + 70° C

## ST26C31

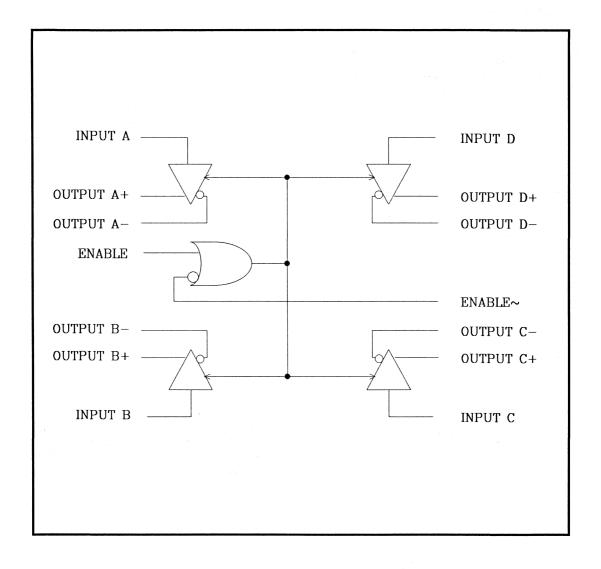

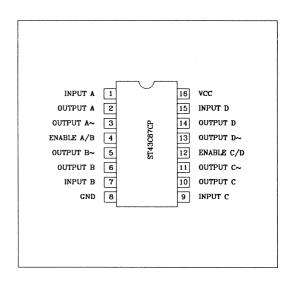

#### QUAD RS-422, RS-423 CMOS DIFFERENTIAL LINE RECEIVER

#### DESCRIPTION

The ST26C32 is a CMOS quad differential line receiver, designed to meet the standard RS-422, RS-423 requirements. The ST26C32 has an input sensitivity of 200mv over the common mode input voltage range of +/- TV. To improve noise margin and output stability for slow changing input signal, special hysteresis is built in the ST26C32 circuit.

#### INPUT A-VCC 16 INPUT A+ INPUT D-15 OUTPUT A INPUT D+ ENABLE OUTPUT D OUTPUT B 12 ENABLE~ INPUT B+ OUTPUT C 6 10 INPUT C+ INPUT B-GND 8 INPUT C-

#### **FEATURES**

- \* Pin-to-pin compatible with National DS26C32C

- \* Low power CMOS design

- \* Three-state outputs with enable pin

- \* Meets the EIA RS-422 requirements

- \* Low propagation delays

- \* High speed

#### **APPLICATIONS**

- \* Hard disk drives

- \* RS-422 controller cards

- \* MFM / RLL controller cards

- \* Differential transmission receiver

#### **GENERAL DESCRIPTION**

The ST26C32 is a high speed line receiver, designed to operate with MFM / RLL controllers and hard disk drives as well as RS-422 and RS-423 differential applications. ST26C32 provides TTL compatible outputs to interface with standard 74LS and CMOS design environments. ST26C32 is suitable for low power 5V operation.

#### ORDERING INFORMATION

Part number

Package

Operating temperature

ST26C32CP16

Plastic

0° C to + 70° C

ST26C32CJ18

PLCC

0° C to + 70° C

## ST26C32

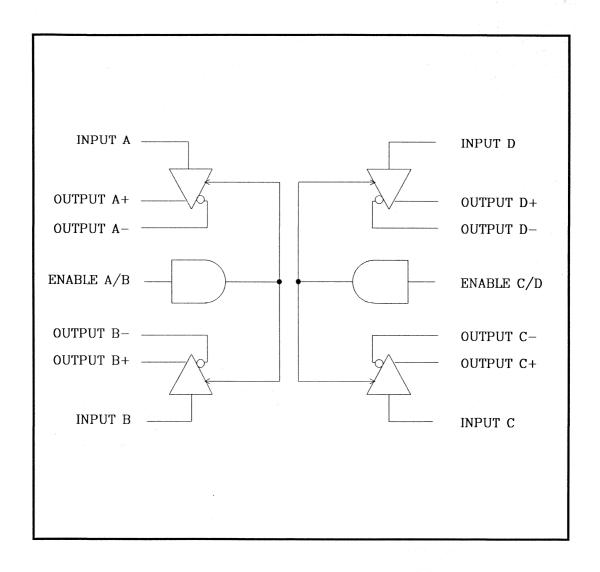

#### QUAD RS-422, RS-423 CMOS DIFFERENTIAL LINE RECEIVER

#### DESCRIPTION

The ST34C86 is a CMOS quad differential line receiver, designed to meet the standard RS-422, RS-423 requirements. The ST34C86 has an input sensitivity of 200mv over the common mode input voltage range of +/- TV. To improve noise margin and output stability for slow changing input signal, special hysteresis is built in the ST34C86 circuit.

#### INPUT A-VCC 16 INPUT A+ INPUT D-OUTPUT A INPUT D+ ENABLE A/B OUTPUT D OUTPUT B 5 12 ENABLE C/D INPUT B+ 11 OUTPUT C INPUT B-10 INPUT C+ INPUT C-GND

#### **FEATURES**

- \* Pin-to-pin compatible with National DS34C86

- \* Low power CMOS design

- \* Three-state outputs with enable pin

- \* Meets the EIA RS-422 requirements

- \* Low propagation delays

- \* High speed

#### **APPLICATIONS**

- \* Hard disk drives

- \* RS-422 controller cards

- \* MFM / RLL controller cards

- \* Differential transmission receiver

#### **GENERAL DESCRIPTION**

The ST34C86 is a high speed line receiver, designed to operate with MFM / RLL controllers and hard disk drives as well as RS-422 and RS-423 differential applications. ST34C86 provides TTL compatible outputs to interface with standard 74LS and CMOS design environments. ST34C86 is suitable for low power 5V operation.

#### ORDERING INFORMATION

Part number ST34C86CP16 ST34C86CJ18 Package Plastic PLCC Operating temperature 0° C to + 70° C

0° C to + 70° C

## ST34C86

## QUAD RS-422, RS-423 CMOS DIFFERENTIAL LINE DRIVER

#### **DESCRIPTION**

The ST34C87 is a CMOS quad differential line driver, designed to meet the standard RS-422, RS-423 requirements and digital data transmission over balanced lines. To improve noise margin and output stability for slow changing input signal special hysteresis is built in the ST34C87 circuit.

#### **FEATURES**

- \* Pin-to-pin compatible with National DS34C87

- \* Low power CMOS design

- \* Three-state outputs with enable pin

- \* Meets the EIA RS-422 requirements

- \* Low propagation delays

- \* High speed

#### **APPLICATIONS**

- \* Hard disk drives

- \* RS-422 controller cards

- \* MFM / RLL controller cards

- \* Digital line transmission driver

#### GENERAL DESCRIPTION

The ST34C87 is a high speed CMOS line driver, designed to operate with MFM / RLL controllers and hard disk drives as well as RS-422 and RS-423 digital data transmission applications. ST34C87 is suitable for low power 5V operation with high input voltage protection devices.

#### ORDERING INFORMATION

Part number

Package

Operating temperature

ST34C87CP16

Plastic

0° C to + 70° C

ST34C87CJ18

PLCC

0° C to + 70° C

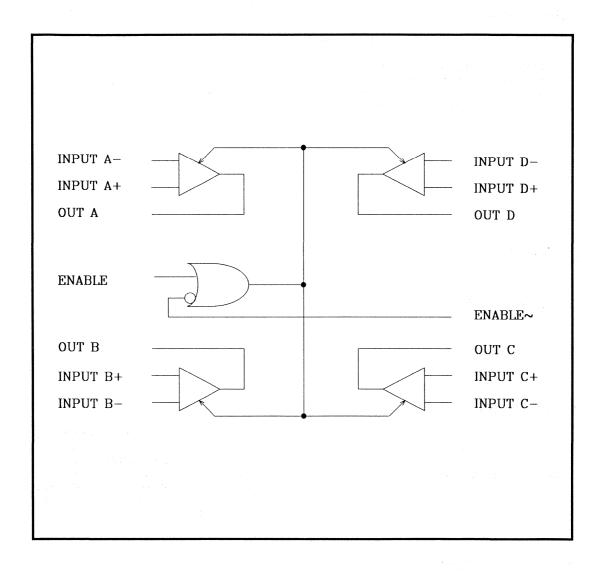

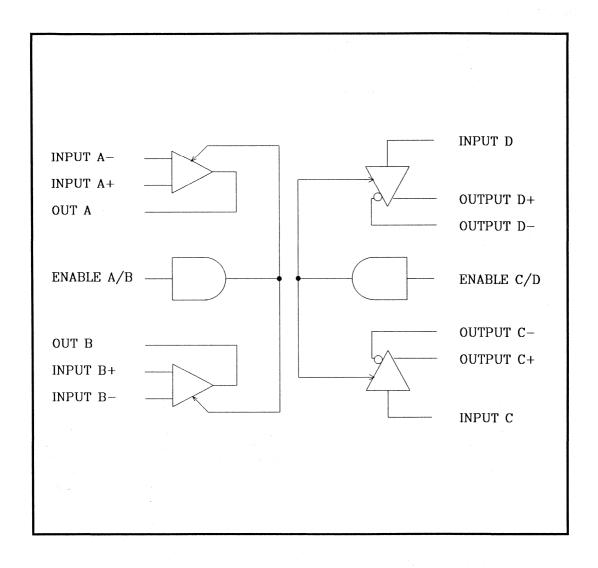

#### **DUAL RS-422, RS-423 CMOS DIFFERENTIAL LINE RECEIVER AND DRIVER**

## DESCRIPTION

The ST86C87 is a CMOS dual differential line receiver and driver, designed to meet the standard RS-422, RS-432 requirements and digital data transmission over balanced lines. The ST86C87 has an input sensitivity of 200mv over the common mode input voltage rage of +/- 7V. To improve noise margin and output stability for slow changing input signal, special hysteresis is built in the ST86C87 circuit.

#### **FEATURES**

- \* Half section of National DS34C86 and DS34C87

- \* Low power CMOS design

- \* Three-state outputs with enable pin

- \* Meets the EIA RS-422 requirements

- \* Low propagation delays

- \* High speed

- \* Dual line receiver with three state control

- \* Dual line driver with three state control

#### INPUT A-VCC 16 INPUT A+ INPUT D OUTPUT A OUTPUT D ENABLE A/B OUTPUT D~ OUTPUT B 12 ENABLE C/D INPUT B+ OUTPUT C~ INPUT B-OUTPUT C 7 INPUT C GND

#### **APPLICATIONS**

- \* Hard disk drives

- \* RS-422 controller cards

- \* MFM / RLL controller cards

- \* Differential transmission receiver and driver

#### ORDERING INFORMATION

Part number

Package

Operationg temperature

ST86C87CP16

Plastic

0° C to + 70° C

ST86C87CJ18

PLCC

0° C to + 70° C

#### **GENERAL DESCRIPTION**

The ST86C87 is a high speed line receiver and driver, designed to operate with MFM / RLL controllers and hard disk drives as well as RS-422 and RS432 differential applications. ST86C87 provides TTL compatible outputs to interface with standard 74LS and CMOS design environments. ST86C87 is suitable for low power 5V operation with Min board space requirements. ST86C87 provides dual differential line receiver with three state control pin and dual line driver with three state control capability.

## ST86C87

# 2

## **MASS STORAGE**

## INTENTIONALLY LEFT BLANK FOR FUTURE EXPANSION

# **UART**

FFR 1001

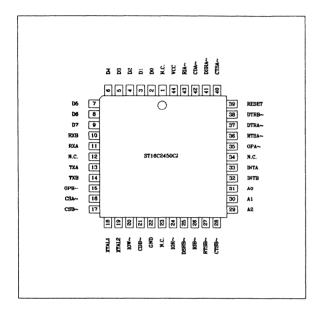

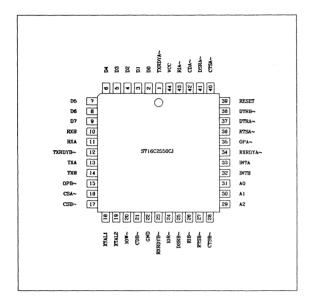

### **ASYNCHRONOUS RECEIVER AND TRANSMITTER**

#### DESCRIPTION

The ST16C450 is a universal asynchronous receiver and transmitter with modem control signals. An internal programmable baud rate generator is provided to select transmit and receive clock rates from 50Hz to 448kHz. The ST16C450 is fabricated in an advanced 1.2 u CMOS process to achieve low drain power and high speed requirements.

#### **FEATURES**

- \* Pin-to-pin and functionally compatible to INS8250, NS16C450

- \* Modem control signals (CTS~, RTS~, DSR~, DTR~, RI~, CD~)

- \* Programmable character lengths (5, 6, 7, 8)

- \* Even, odd, or no parity bit generation and detection

- \* Status report register

- \* Independent transmit and receive control

- \* TTL compatible inputs, outputs

- \* 448 kHz transmit/receive operation with 7.372 MHz crystal or external clock source.

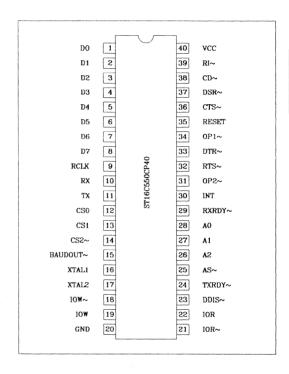

#### DO 1 40 VCC 2 39 D1 RI~ 3 38 D2 CD~ 4 37 D3 DSR~ 5 36 CTS~ D4 6 35 D5 RESET 7 34 0P1~ D6 8 33 DTR~ D7 RCLK 9 32 RTS~ T16C450CP40 RX 10 31 0P2~ ΤX 11 30 INT CSO 12 29 NC 13 CS1 28 AO 27 CS2~ 14 A1 BAUDOUT~ 26 A2 16 25 AS~ XTAL1 24 17 XTAL2 CSOUT 18 23 IOW~ DDIS~ IOW 19 22 IOR GND IOR~

#### **APPLICATIONS**

- \* Serial receiver or transmitter

- \* Serial to parallel/parallel to serial converter

- \* Modem with/without handshaking signals

- \* Terminal

#### ORDERING INFORMATION

Part number

Package

Operating temperature

ST16C450CP40

Plastic

0° C to +70° C

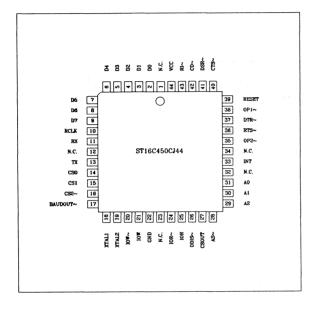

ST16C450CJ44

PLCC

0° C to +70° C

#### **GENERAL DESCRIPTION**

The ST16C450 is an improved version of the INS8250/NS16C450 UART with higher speed operating access time. The ST16C450 performs the parallel to serial/serial to parallel conversion on the data characters received from the CPU or the MODEM. The on board status register will provide the error conditions, type and status of the transfer operations being performed. Complete MODEM control capability, and a processor interrupt system that may be software tailored to the user's requirements to minimize the computing required to handle the communications link. The ST16C450 can interface easily to the most popular microprocessors, and communications link faults can be detected with internal loopback capability.

## ST16C450

#### **SYMBOL DESCRIPTION**

| Symbol   | Pin | Signal type                             | Pin description                                                                                                                                                                                                                                                                                                                  |

|----------|-----|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7    | 1-8 | 1/0                                     | Bidirectional data bus. Eight bit, three state data bus to transfer information to or from the CPU. Do is the least significant bit of the data bus and the first serial data bit to be received or transmitted.                                                                                                                 |

| RCLK     | 9   | <b>1</b>                                | Receiver clock input. The external clock input to the ST16C450 receiver section.                                                                                                                                                                                                                                                 |

| RX       | 10  | <b>1</b>                                | Serial data input. The serial information received from MODEM or RS232 to ST16C450 receive circuit. A mark (high) is logic one and a space (low) is logic zero. During the local loopback mode the RX input is disabled from external connection and connected to the TX output internally.                                      |

| тх       | 11  | 0                                       | Serial data output. The serial data is transmitted via this pin with additional start, stop and parity bits. The TX will be held in mark (high) state during reset, local loopback mode or when the transmitter is disabled.                                                                                                     |

| CS0      | 12  | ı                                       | Chip select 1. (active high) A high at this pin (while CS1=1 and CS2=0) will enable the UART/CPU data transfer operation.                                                                                                                                                                                                        |

| CS1      | 13  | 1                                       | Chip select 2. (active high) A high at this pin (while CS0=1 and CS2=0) will enable the UART/CPU data transfer operation.                                                                                                                                                                                                        |

| CS2~     | 14  | l                                       | Chip select 3. (active low) A low at this pin (while CS0=1 and CS1=1) will enable the UART / CPU data transfer operation.                                                                                                                                                                                                        |

| BAUDOUT~ | 15  | 0                                       | Baud rate generator clock output. This output provides the 16x clock of the internal selected baud rate.                                                                                                                                                                                                                         |

| XTAL1    | 16  | 1 · · · · · · · · · · · · · · · · · · · | Crystal input 1 or external clock input. A crystal can be connected to this pin and XTAL2 pin to utilize the internal oscillator circuit. An external clock can be used to clock internal circuit and baud rate generator for custom transmission rates.                                                                         |

| XTAL2    | 17  |                                         | Crystal input 2. See XTAL1.                                                                                                                                                                                                                                                                                                      |

| IOW~     | 18  | 1                                       | Write strobe. (active low) A low on this pin will transfer the contents of the CPU data bus to the addressed register.                                                                                                                                                                                                           |

| IOW      | 19  |                                         | Write strobe. (active high) Same as IOW $\sim$ , but uses active high input. Note that only an active IOW $\sim$ or IOW input is required to transfer data from CPU to ST16C450 during write operation ( while CS0 = 1, CS1 = 1 and CS2 $\sim$ = 0). The unused pin should be tied to VCC or GND( IOW=GND or IOW $\sim$ = VCC ). |

| GND      | 20  | 0                                       | Signal and power ground.                                                                                                                                                                                                                                                                                                         |

## ST16C450

#### **SYMBOL DESCRIPTION**

| Symbol | Pin | Signal type | Pin description                                                                                                                                                                                                                                                      |

|--------|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOR~   | 21  |             | Read strobe. (active low) A low level on this pin (while $CS0 = 1$ , $CS1 = 1$ and $CS2 \sim = 0$ ) will transfer the contents of the ST16C450 data bus to the CPU.                                                                                                  |

| IOR    | 22  | l           | Read strobe. (active high) Same as IOR~, but uses active high input. Note that only an active IOR~ or IOR input is required to transfer data from ST16C450 to CPU during read operation (while CS0=1, CS1=1 and CS2~=0). The unused pin should be tied to VCC or GND |

|        |     |             | (IOR=GND or IOR~=VCC).                                                                                                                                                                                                                                               |

| DDIS~  | 23  | 0           | Drive disable. (active low) This pin goes low when CPU is reading data from ST16C450 to disable the external transceiver or logics.                                                                                                                                  |

| CSOUT  | ,24 | ) O         | Chip select out. A high on this pin indicates that the chip has been selected by the chip select input pins.                                                                                                                                                         |

| AS~    | 25  | 1           | Address strobe. (active low) A low on this pin will latch the state of the chip selects and addressed register.                                                                                                                                                      |

| A2     | 26  | l           | Address line 2. To select internal registers.                                                                                                                                                                                                                        |

| :A1    | 27  | 1           | Address line 1. To select internal registers.                                                                                                                                                                                                                        |

| A0     | 28  | I           | Address line 0. To select internal registers.                                                                                                                                                                                                                        |

| INT    | 30  | 0           | Interrupt output. (active high) This pin goes high (when enabled by the interrupt enable register) whenever a receiver error, receiver data available, transmitter empty or modem status condition flag is detected.                                                 |

| OP2~   | 31  | 0           | General purpose output. (active low) User defined output. See bit-3 modem control register.                                                                                                                                                                          |

| RTS~   | 32  | 0           | Request to send. (active low) To indicate the transmitter has data ready to send. Writing a "1" in the modem control register (MCR bit-1) will set this pin to low state. After the reset this pin will be set to high.                                              |

| DTR~   | 33  | 0           | Data terminal ready. (active low) To indicate that ST16C450 is ready to receive data. This pin can be controlled via the modem control register (MCR bit-0). Writing a "1" at the MCR bit-0 will set the DTR~                                                        |

|        |     |             | output to low. This pin will be set to high state after writing a "0" to that register or after the reset.                                                                                                                                                           |

| OP1~   | 34  | O           | General purpose output. (active low) User defined output. See bit-2 of modem control register.                                                                                                                                                                       |

|        |     |             |                                                                                                                                                                                                                                                                      |

#### SYMBOL DESCRIPTION

| Symbol | Pin | Signal type | Pin description                                                                                                                                                                      |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET  | 35  | _           | Master reset. (active high) A high on this pin will reset all the outputs and internal registers. The transmitter output and the receiver input will be disabled during reset time.  |

| стѕ~   | 36  | - 1         | Clear to send. (active low) The CTS~ signal is a MODEM control function input whose conditions can be tested by reading the MSR BIT-4. CTS~ has no effect on the transmitter output. |

| DSR~   | 37  | <b>1</b>    | Data set ready. (active low) A low on this pin indicates that MODEM is ready to exchange data with UART.                                                                             |

| CD~    | 38  | •           | Carrier detect. (active low) A low on this pin indicates that a carrier has been detected by the modern.                                                                             |

| RI~    | 39  | 1           | Ring detect indicator. (active low) A low on this pin indicates that modem has received a ringing signal from telephone line.                                                        |

| vcc    | 40  | 1           | Power supply input.                                                                                                                                                                  |

#### PROGRAMMING TABLE

| DLAB                                           | A2                                        | A1                                   | A0                                   | READ MODE                                                                                                         | WRITE MODE                                                                                                                                                     |

|------------------------------------------------|-------------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>1 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | Receive Holding Register Interrupt Status Register Line Status Register Modem Status Register Scratchpad Register | Transmit Holding Register Interrupt Enable Register Line Control Register Modem Control Register Scratchpad Register LSB of Divisor Latch MSB of Divisor Latch |

#### REGISTER FUNCTIONAL DESCRIPTION

#### TRANSMIT AND RECEIVE HOLDING REGISTER

The serial transmitter section consists of a Transmit Hold Register and Transmit Shift Register. The status of the transmit hold register is provided in the Line Status Register. Writing to this register will transfer the contents of data bus (D7-D0) to the transmit holding register whenever the transmitter holding register or transmitter shift register is empty. The transmit holding register empty flag will be set to "1" when the transmitter is empty or data is transfered to the transmit shift register. Note that a write operation should be per-

formed when the transmit holding register empty flag is set. On the falling edge of the start bit, the receiver internal counter will start to count 7 1/2 clocks (16x clock) which is the center of the start bit. The start bit is valid if the RX is still low at the mid-bit sample of the start bit. Verifying the start bit prevents the receiver from assembling a false data character due to a low going noise spike on the RX input. Receiver status codes will be posted in the Line Status Register.

## ST16C450

#### **ST16C450 ACCESSIBLE REGISTERS**

| A2 | A1 | A0 | Register | BIT-7                      | BIT-6           | BIT-5                      | BIT-4              | ВІТ-3                        | BIT-2                     | BIT-1                           | BIT-0                          |

|----|----|----|----------|----------------------------|-----------------|----------------------------|--------------------|------------------------------|---------------------------|---------------------------------|--------------------------------|

| 0  | 0  | 0  | RHR      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                     | bit-1                           | bit-0                          |

| 0  | 0  | 0  | THR      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                     | bit-1                           | bit-0                          |

| 0  | 0  | 1  | IER      | 0                          | 0               | 0                          | 0                  | modem<br>status<br>interrupt | receive<br>line<br>status | transmit<br>holding<br>register | receive<br>holding<br>register |

| 0  | 1  | 0  | ISR      | 0                          | 0               | 0                          | 0                  | 0                            | int<br>priority<br>bit-1  | int<br>priority<br>bit-0        | int<br>status                  |

| 0  | 1  | 1  | LCR      | divisor<br>latch<br>enable | set<br>break    | set<br>parity              | even<br>parity     | parity<br>enable             | stop<br>bits              | word<br>length<br>bit-1         | word<br>length<br>bit-0        |

| 1  | 0  | 0  | MCR      | 0                          | 0               | 0                          | loop<br>back       | OP2~                         | OP1~                      | RTS~                            | DTR~                           |

| 1  | 0  | 1  | LSR      | 0                          | trans.<br>empty | trans.<br>holding<br>empty | break<br>interrupt | framing<br>error             | parity<br>error           | overrun<br>error                | receive<br>data<br>ready       |

| 1  | 1  | 0  | MSR      | CD                         | RI              | DSR                        | CTS                | delta<br>CD~                 | delta<br>RI~              | delta<br>DSR~                   | delta<br>CTS~                  |

| 1  | 1  | 1  | SPR      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                     | bit-1                           | bit-0                          |

| 0  | 0  | 0  | DLL      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                     | bit-1                           | bit-0                          |

| 0  | 0  | 1  | DLM      | bit-15                     | bit-14          | bit-13                     | bit-12             | bit-11                       | bit-10                    | bit-9                           | bit-8                          |

#### **INTERRUPT ENABLE REGISTER (IER)**

The Interrupt Enable Register (IER) masks the incoming interrupts from receiver ready, transmitter empty, line status and modem status registers to the INT output pin.

#### IER BIT-0:

0 = disable the receiver ready interrupt 1 = enable receiver ready interrupt

#### IER BIT-1:

0 = disable transmitter empty interrupt 1 = enable transmitter empty interrupt

#### IER BIT-2:

0 = disable receiver line status interrupt 1 = enable receiver line status interrupt

#### IER BIT-3:

0 = disable the modem status register interrupt 1 = enable the modem status register interrupt

#### **IER BIT 7-4:**

All these bits are set to logic zero.

#### **INTERRUPT STATUS REGISTER (ISR)**

The ST16C450 provides four level prioritized interrupt conditions to minimize software overhead during data character transfers. The Interrupt Status Register (ISR) provides the source of the interrupt in prioritized matter. During the read cycle the ST16C450 provides the highest interrupt level to be serviced by CPU, no other interrupts are acknowledged until the particular interrupt is serviced. The following are the prioritized interrupt levels:

| Pric | ority | leve | el | Source of the interrupts                                |

|------|-------|------|----|---------------------------------------------------------|

| Р    | D2    | D1   | D0 |                                                         |

| 1    | 1     | 1    | 0  | LSR (Receiver Line Status<br>Register)                  |

| 2    | 1     | 0    | 0  | RXRDY (Received Data                                    |

| 3    | 0     | - 1  | 0  | Ready)<br>TXRDY (Transmitter Holding<br>Register Empty) |

| 4    | 0     | 0    | 0  | MSR (Modern Status Register)                            |

#### ISR BIT-0:

0 = an interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt service routine.

1 = no interrupt pending

#### ISR BIT 1-2:

Logical combination of these bits, provides the highest priority interrupt pending.

#### **ISR BIT 3-7:**

These bits are not used and are set to zero.

#### LINE CONTROL REGISTER (LCR)

The Line Control Register is used to specify the asynchronous data communication format. The number of the word length, stop bits, and parity can be selected by writing appropriate bits in this register.

#### LCR BIT1-0:

These two bits specify the word length to be transmitted or received.

00=5 bits word length

01 = 6 bits word length

10=7 bits word length

11 = 8 bits word length

#### LCR BIT-2:

The number of stop bits can be specified by this bit.

0=1 stop bit, when word length=5, 6, 7, 8 bits

1=1 and 1/2 stop bit, when word length=5 bits

1=2 stop bits, word length=6, 7, 8 bits

#### LCR BIT-3:

Parity or no parity can be selected via this bit. 0 = no parity

1 = a parity bit is generated during the transmission, receiver also checks for received parity.

#### LCR BIT-4:

If the parity bit is enabled, LCR BIT-4 selects the even or odd parity format.

0 = odd parity is generated by calculating odd number of 1's in the transmitted data, receiver also checks for same format.

1 = an even parity bit is generated by calculating the number of even 1's in the transmitted data, receiver also checks for same format.

#### LCR BIT-5:

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5=1 and LCR bit-4=0, parity bit is forced to "1" in the transmitted and received data.

LCR BIT-5=1 and LCR bit-4=1, parity bit is forced to "0" in the transmitted and received data.

#### LCR BIT-6:

Break control bit.

1 = forces the transmitter output (TX) to go low to

## ST16C450

alert the communication terminal 0=normal operating condition

#### LCR BIT-7:

The internal baud rate counter latch enable (DLAB) 0 = normal operation

1 = select divisor latch register

#### **MODEM CONTROL REGISTER (MCR)**

This register controls the interface with the MODEM or a peripheral device (RS232).

#### MCR BIT-0:

0=force DTR~ output to high 1=force DTR~ output to low

#### MCR BIT-1:

0=force RTS~ output to high 1=force RTS~ output to low

#### MCR BIT-2:

0=set OP1~ output to high 1=set OP1~ output to low

#### MCR BIT -3:

0=set OP2~ output to high 1=set OP2~ output to low

#### MCR BIT -4:

0=normal operating mode

1=enable local loop-back mode (diagnostics). The transmitter output (TX) is set high (mark condition), the receiver input (RX) , CTS ~, DSR ~, CD ~, and RI ~ are disabled. Internally transmitter output is connected to the receiver input and DTR ~, RTS ~, OP1 ~, and OP2 ~ are connected to modem control inputs. In this mode , the receiver and transmitter interrupts are fully operational. The Modem Control Interrupts are also operational, but the interrupts sources are now the lower four bits of the Modem Control Register instead of the four Modem Control inputs. The interrupts are still controlled by the IER .

#### MCR BIT 5-7:

Not used. Are set to zero permanently.

#### LINE STATUS REGISTER (LSR)

This register provides the status of data transfer to CPU.

#### LSR BIT-0:

0 = no data in receive holding register

1 = data has been received and saved in the receive holding register

#### LSR BIT-1:

0 = no overrun error (normal)

1 = overrun error, next character arrived before receive holding register was empty

#### LSR BIT-2:

0 = no parity error (normal)

1 = parity error, received data does not have correct parity information

#### LSR BIT-3:

0 = no framing error (normal)

1 = framing error received, received data did not have a valid stop bit

#### LSR BIT-4:

0 = no break condition (normal)

1 = receiver received a break signal (RX was low for one character time frame)

#### LSR BIT-5:

0=transmit holding register is full. ST16C450 will not accept any data for transmission

1 = transmit holding register is empty. CPU can load the next character

#### LSR BIT-6:

0 = transmitter holding and shift registers are full

1 = transmitter holding and shift registers are empty

#### LSR BIT-7:

Not used. Set to zero permanently.

#### MODEM STATUS REGISTER (MSR)

This register provides the current state of the control lines from the modem or peripheral to the CPU. Four bits of this register are used to indicate the changed information. These bits are set to "1" whenever a control input from the MODEM changes state. They are set to "0" whenever the CPU reads this register.

#### MSR BIT-0:

Indicates that the CTS~ input to the ST16C450 has changed state since the last time it was read.

### MSR BIT-1:

Indicates that the DSR $\sim$  input to the ST16C450 has changed state since the last time it was read.

### MSR BIT-2:

Indicates that the RI~ input to the ST16C450 has changed from a low to a high state.

### MSR BIT-3:

Indicates that the CD~ input to the ST16C450 has changed state since the last time it was read.

### MSR BIT-4:

This bit is equivalent to RTS in the MCR. It is the compliment of the CTS~ input.

### MSR BIT-5:

This bit is equivalent to DTR in the MCR. It is the compliment of the DSR~ input.

### MSR BIT-6:

This bit is equivalent to OP1 in the MCR. It is the compliment of the RI  $\sim$  input.

### MSR BIT-7:

This bit is equivalent to OP2 in the MCR. It is the compliment to the  $CD \sim input$ .

### SCRATCHPAD REGISTER (SR)

ST16C450 provides a temporary data register to store 8 bits of information for variable use.

## BAUD RATE GENERATOR PROGRAMMING TABLE (1.8432MHz crystal or external clock)

| BAUD RATE | 16 x CLOCK DIVISOR | % ERROR |

|-----------|--------------------|---------|

| 50        | 2304               |         |

| 110       | 1047               | 0.026   |

| 150       | 768                |         |

| 300       | 384                |         |

| 600       | 192                |         |

| 1200      | 96                 | 1       |

| 2400      | 48                 |         |

| 4800      | 24                 |         |

| 7200      | 16                 |         |

| 9600      | 12                 |         |

| 19.2K     | 6                  |         |

| 38.4K     | 3                  |         |

| 56K       | 2                  | 2.86    |

| 112K      | 1                  |         |

### ST16C450 RESET CONDITION TABLE

| REGISTERS                       | RESET STATE                                                                                                                                                     |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IER<br>ISR<br>LCR<br>MCR<br>LSR | IER BITS 0-7=0 ISR BIT-0=1, ISR BITS 1-7=0 LCR BITS 0-7=0 MCR BITS 0-7=0 LSR BITS 0-4=0, LSR BITS 5-6=1 LSR, BIT 7=0 MSR BITS 0-3=0, MSR BITS 4-7=input signals |

| SIGNALS | RESET STATE  |

|---------|--------------|

| TX      | High         |

| OP1~    | High         |

| OP2~    | High         |

| RTS~    | High         |

| DTR~    | High         |

| INT     | BITS 0-3=low |

|         | 1            |

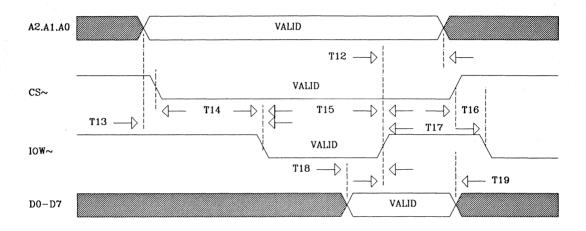

## **AC ELECTRICAL CHARACTERISTICS**

$T_A$ =25° C,  $V_{CC}$ =5.0 V  $\pm$  5% unless otherwise specified.

| Symbol                             | Parameter                                                           | Parameter Limits                      |  |    | Units    | Conditions     |

|------------------------------------|---------------------------------------------------------------------|---------------------------------------|--|----|----------|----------------|

| *:                                 | min typ max                                                         |                                       |  |    |          |                |

|                                    |                                                                     |                                       |  |    | 1 1      |                |

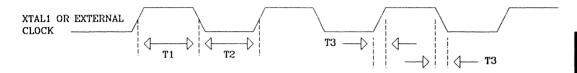

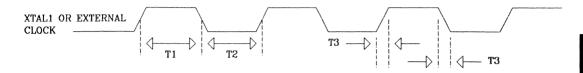

| T,                                 | Clock high pulse duration                                           | 60                                    |  |    | ns       |                |

| T <sub>2</sub>                     | Clock low pulse duration                                            | 60                                    |  |    | ns       | External clock |

| T <sub>3</sub>                     | Clock rise/fall time                                                |                                       |  |    | "        |                |

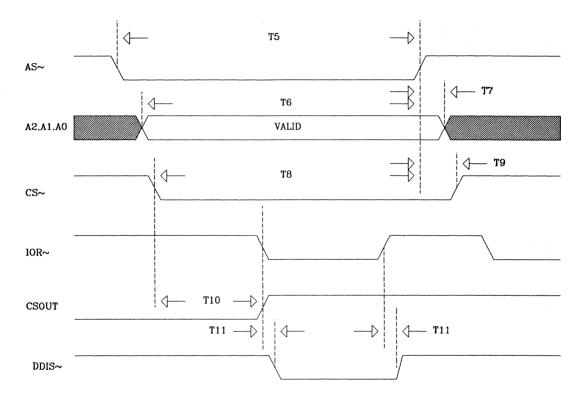

| T <sub>5</sub>                     | Address strobe width                                                | 30                                    |  |    | ns       |                |

| T <sub>6</sub>                     | Address setup time                                                  | 30                                    |  |    | ns       |                |

| T <sub>7</sub>                     | Address hold time                                                   | 5                                     |  |    | ns       |                |

| T <sub>8</sub>                     | Chip select setup time                                              | 25                                    |  |    | ns       |                |

| T <sub>s</sub>                     | Chip select hold time                                               | 0                                     |  |    | ns       |                |

| T <sub>10</sub>                    | Chip select output delay                                            | -                                     |  | 50 | ns       | 100 pF load    |

| - 10                               | from select                                                         |                                       |  |    |          |                |

| T <sub>11</sub>                    | IOR~ to drive disable delay                                         |                                       |  | 35 | ns       | 100 pF load    |

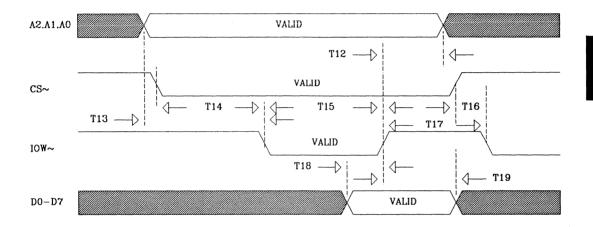

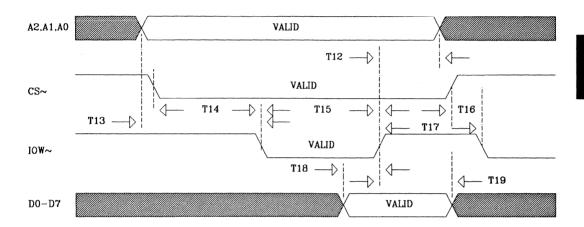

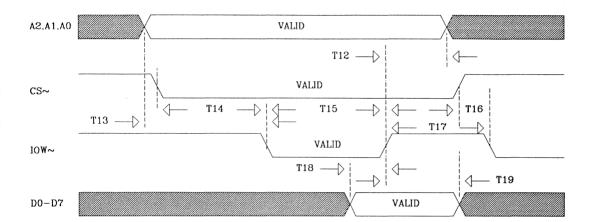

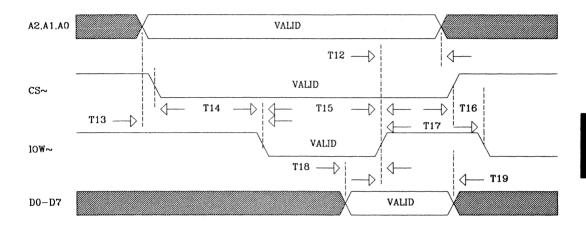

| T <sub>12</sub>                    | Address hold time from IOW~                                         | 5                                     |  |    | ns       | Note: 1        |

| T <sub>13</sub>                    | IOW~ delay from address                                             | 25                                    |  |    | ns       | Note: 1        |

| T <sub>14</sub>                    | IOW~ delay from                                                     | 10                                    |  |    | ns       | Note: 1        |

| т                                  | IOW~ strobe width                                                   | 50                                    |  |    | ns       |                |

| T <sub>15</sub><br>T <sub>16</sub> | Chip select hold time                                               | 5                                     |  |    | ns       | Note: 1        |

| 16                                 | from IOW~                                                           | 3                                     |  |    | 115      | Note. 1        |

| T <sub>17</sub>                    | Write cycle delay                                                   | 55                                    |  |    | ns       |                |

| Tw                                 | Write cycle=T <sub>15</sub> +T <sub>17</sub>                        | 135                                   |  |    | ns       |                |

| T <sub>18</sub>                    | Data setup time                                                     | 10                                    |  |    | ns       |                |

| T <sub>19</sub>                    | Data hold time                                                      | 25                                    |  |    | ns       |                |

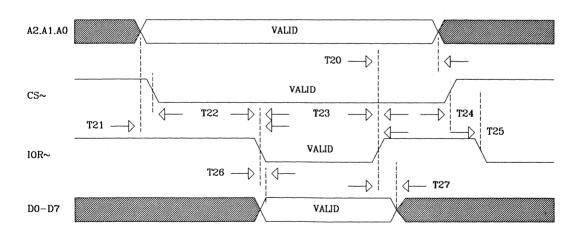

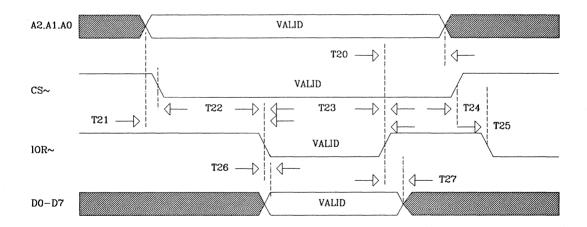

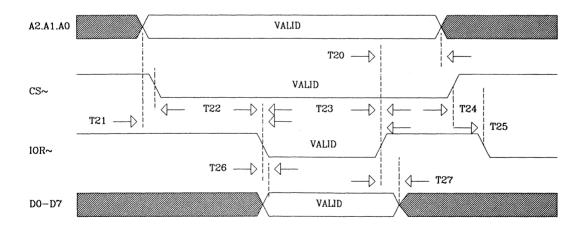

| T <sub>20</sub>                    | Address hold time from IOR~                                         | 0                                     |  |    | ns       | Note: 1        |

| T <sub>21</sub>                    | IOR~ delay from address                                             | 10                                    |  |    | ns       | Note: 1        |

| T <sub>22</sub>                    | IOR~ delay from                                                     | 10                                    |  |    | ns       | Note: 1        |

| T <sub>23</sub>                    | IOR~ strobe width                                                   | 75                                    |  |    | ns       |                |

| T <sub>24</sub>                    | Chip select hold time from                                          | 0                                     |  |    | ns       | Note: 1        |

| T                                  | IOR~<br>Read cycle delay                                            | E0.                                   |  |    |          |                |

| T <sub>25</sub><br>Tr              |                                                                     | 50                                    |  |    | ns       |                |

|                                    | Read cycle=T <sub>23</sub> +T <sub>25</sub> Delay from IOR~ to data | 135                                   |  | 75 | ns       | 100 pF load    |

| T <sub>26</sub>                    | IOR~ to floating                                                    | 0                                     |  | 50 | ns<br>ns | 100 pF load    |

| T <sub>27</sub>                    | data delay                                                          | U                                     |  | 50 | l iis    | TOU PE TOAU    |

|                                    |                                                                     |                                       |  |    |          |                |

|                                    |                                                                     | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |  |    |          |                |

|                                    |                                                                     | <u> </u>                              |  |    |          | *              |

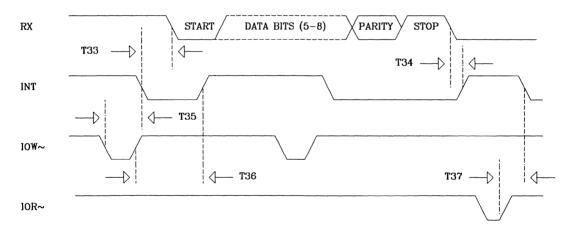

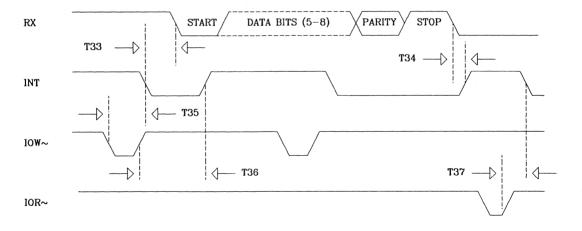

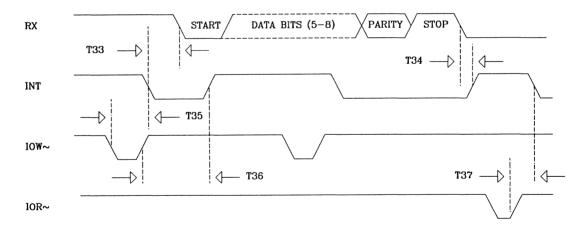

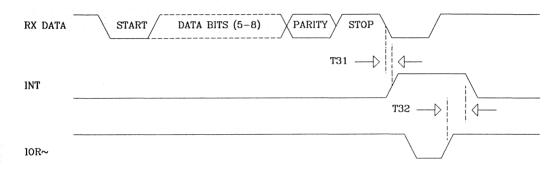

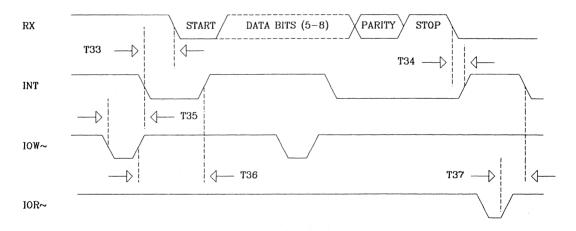

## **AC ELECTRICAL CHARACTERISTICS**

$T_A = 25^{\circ}$  C,  $V_{CC} = 5.0$  V  $\pm$  5% unless otherwise specified.

| Symbol          | Parameter                                      | Limits |     |                   | Units          | Conditions  |

|-----------------|------------------------------------------------|--------|-----|-------------------|----------------|-------------|

|                 |                                                | min    | typ | max               |                |             |

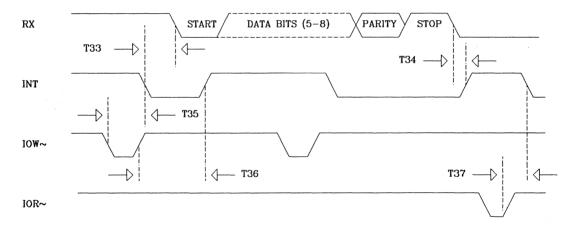

| RANSMI          | TTER                                           |        |     |                   | ,              |             |

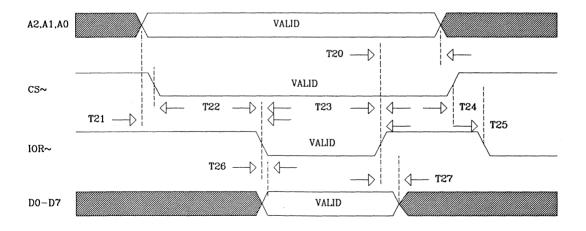

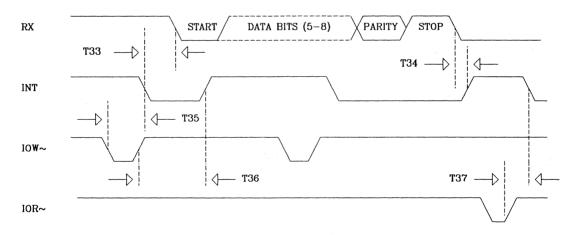

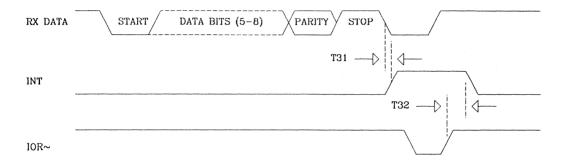

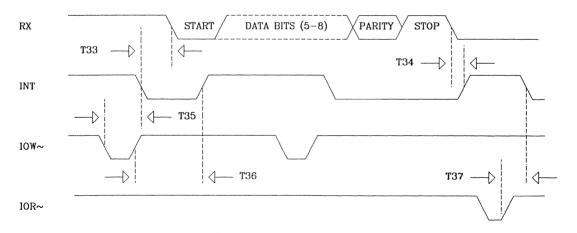

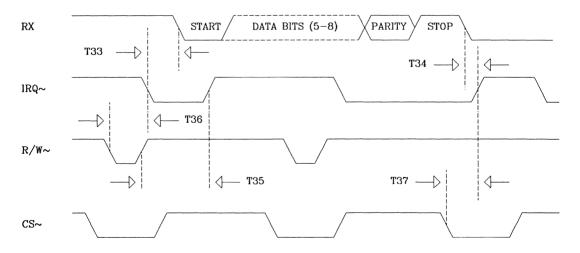

| T <sub>33</sub> | Delay from initial INT reset to transmit start | 8      |     | 24                | , i <b>*</b> 7 |             |

| T <sub>34</sub> | Delay from stop to interrupt                   |        |     | 100               | ns             |             |

| T <sub>35</sub> | Delay from IOW~                                |        |     |                   |                |             |

| T <sub>36</sub> | Delay from initial Write<br>to interrupt       | 16     |     | 24                | *              |             |

| T <sub>37</sub> | Delay from IOR~<br>to reset interrupt          |        |     | 75                | ns             | 100 pF load |

|                 |                                                |        |     |                   |                |             |

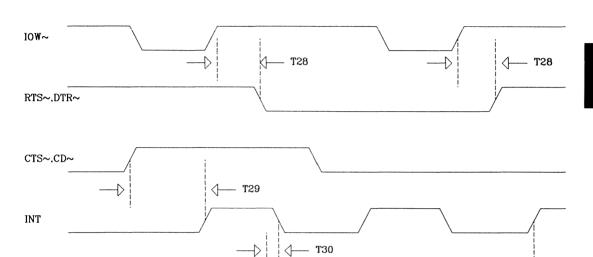

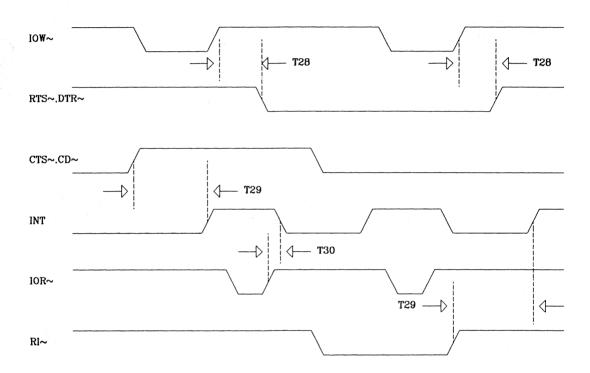

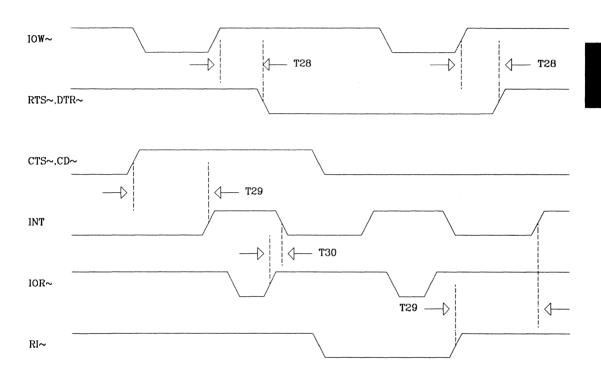

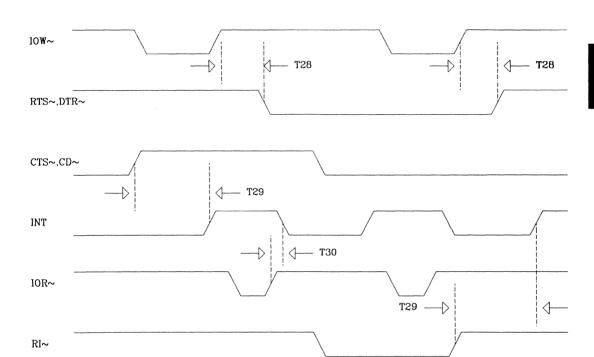

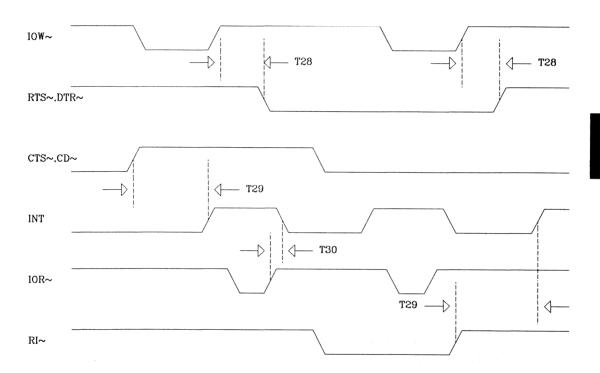

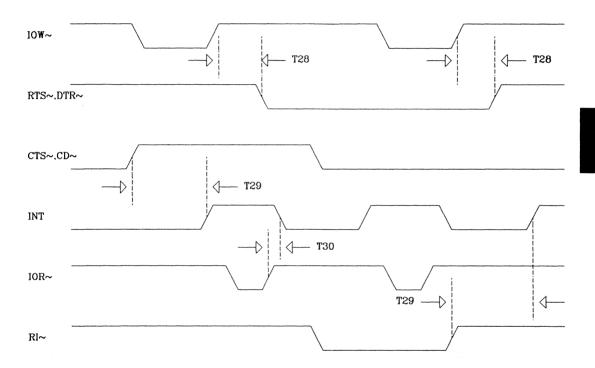

| MODEM           | CONTROL                                        |        |     |                   | ·              |             |

| T <sub>28</sub> | Delay from IOW~<br>to output                   |        | -   | 50                | ns             | 100 pF load |

| T <sub>29</sub> | Delay to set interrupt<br>from MODEM input     |        |     | 70                | ns             | 100 pF load |

| T <sub>30</sub> | Delay to reset interrupt<br>from IOR~          |        | ~   | 70                | ns             | 100 pF load |

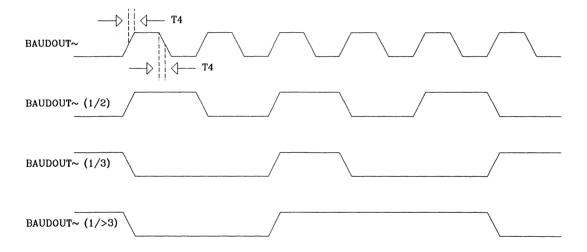

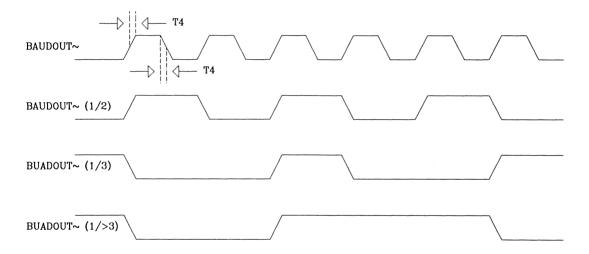

| BAUD RA         | ATE GENERATOR                                  |        |     |                   |                |             |

| Ñ               | Baud rate devisor                              | 1      |     | 216-1             |                | 100         |

| T <sub>4</sub>  | Baud out negative<br>edge delay                |        |     | 100               | ns             | 100 pF load |

| T <sub>4</sub>  | Baud out positive edge delay                   |        |     | 100               | ns             | 100 pF load |

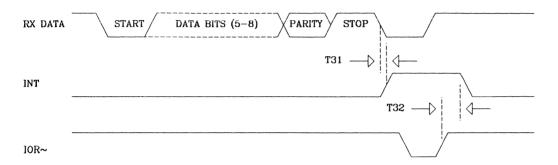

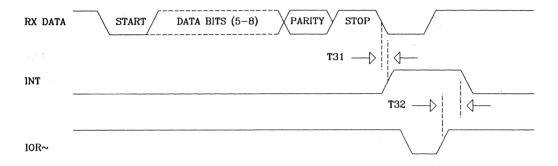

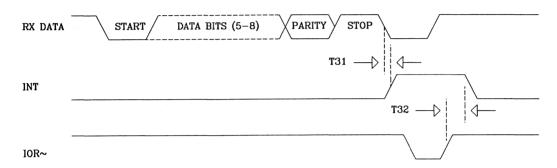

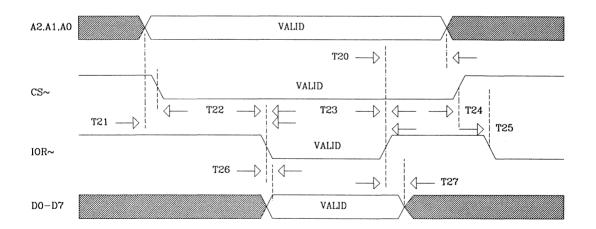

| RECEIVI         | ER                                             |        |     |                   | A              |             |

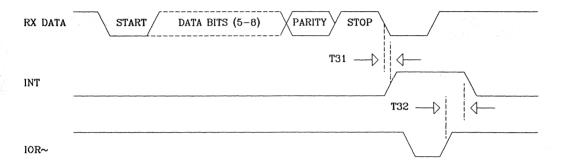

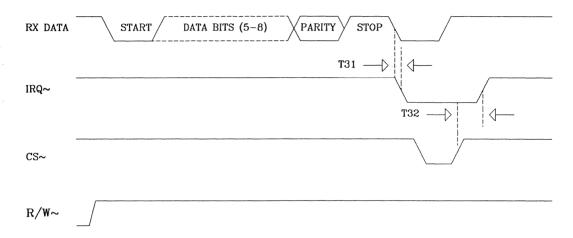

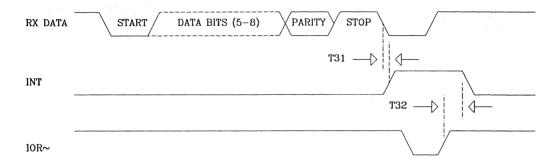

| T <sub>31</sub> | Delay from stop to set                         |        |     | 1 <sub>Rclk</sub> | ns             | 100 pF load |

| T <sub>32</sub> | interrupt Delay from IOR~ to reset interrupt   |        |     | 200               | ns             | 100 pF load |

Applicable only when AS  $\sim$  is tied low Baudout  $\sim$  cycle Note 1:

## **ABSOLUTE MAXIMUM RATINGS**

Operating supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts ± 5% GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

## **DC ELECTRICAL CHARACTERISTICS**

$T_A = 25^{\circ}$  C,  $V_{CC} = 5.0$  V  $\pm$  5% unless otherwise specified.

| Symbol                             | Parameter                                                                                                                                 |                                   | Limits |                                 | Units                  | Conditions                                                       |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|---------------------------------|------------------------|------------------------------------------------------------------|

|                                    |                                                                                                                                           | min                               | typ    | max                             |                        |                                                                  |

| VILCK VIHCK VIL VIH VOL VOH ICC    | Clock input low level Clock input high level Input low level Input high level Output low level Output high level Avg power supply current | -0.5<br>3.0<br>-0.5<br>2.2<br>2.4 |        | 0.6<br>VCC<br>0.8<br>VCC<br>0.4 | V<br>V<br>V<br>V<br>mA | I <sub>OL</sub> = 6 mA on all outputs<br>I <sub>OH</sub> = -6 mA |

| l <sub>iL</sub><br>l <sub>CL</sub> | Input leakage<br>Clock leakage                                                                                                            |                                   |        | ±10<br>±10                      | uA<br>uA               |                                                                  |

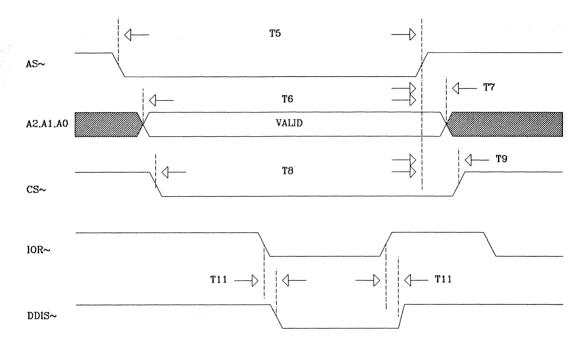

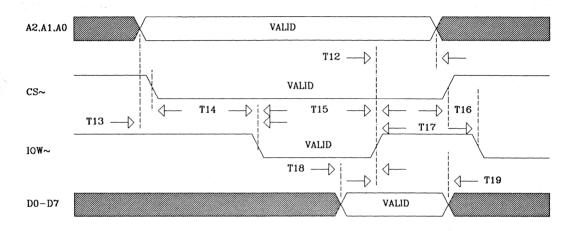

### **TIMING DIAGRAM**

## CLOCK TIMING

## BAUDOUT~ TIMING

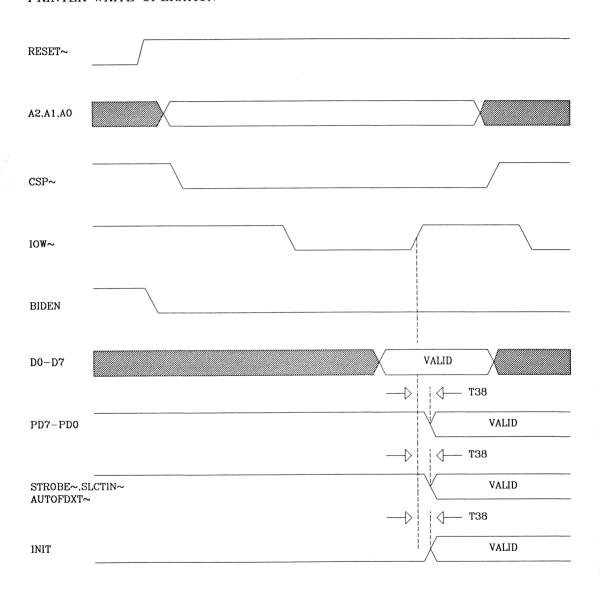

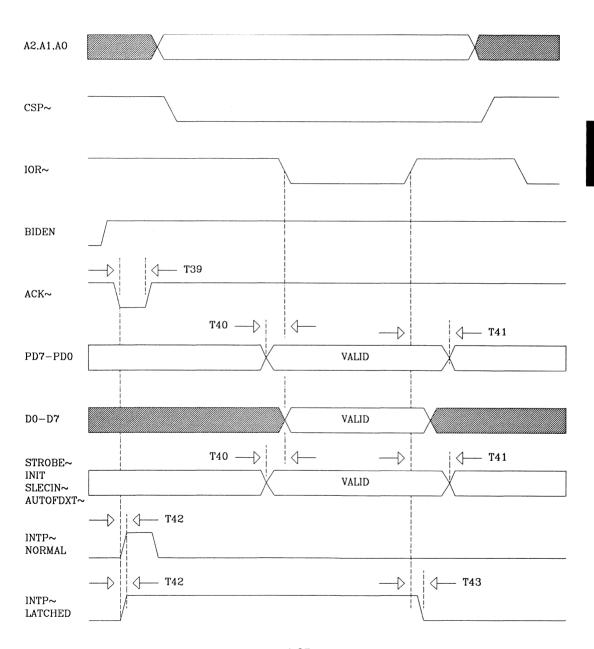

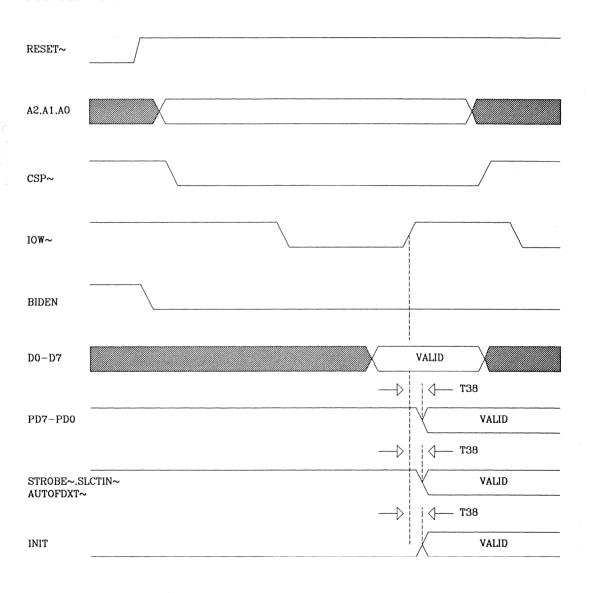

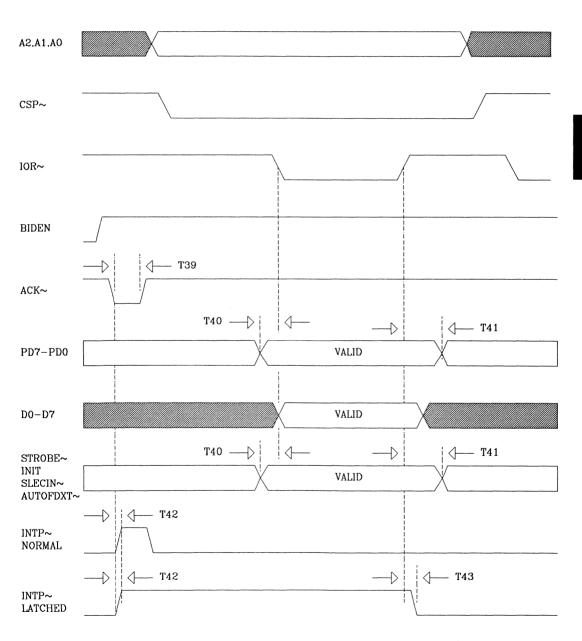

## **TIMING DIAGRAM**

## GENERAL TIMING

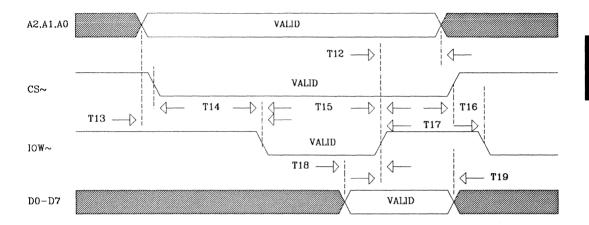

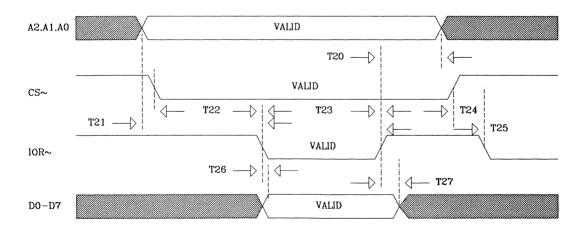

## **TIMING DIAGRAM**

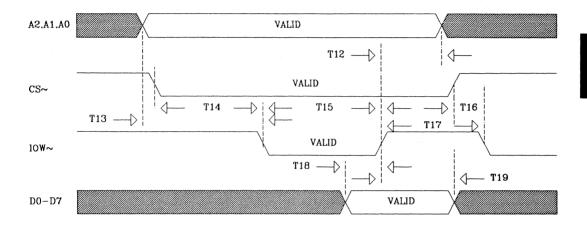

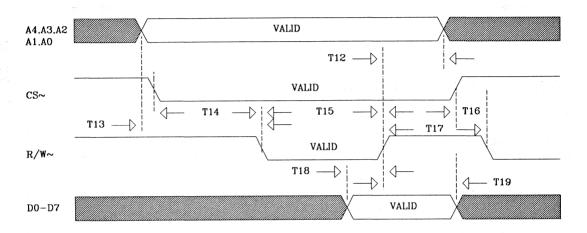

## WRITE CYCLE TIMING

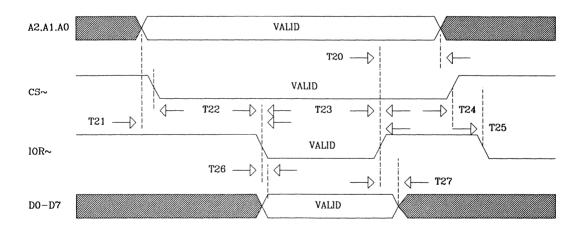

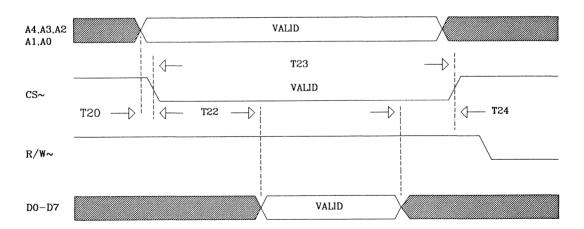

## READ CYCLE TIMING

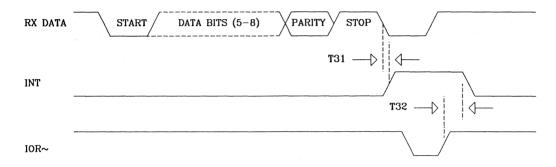

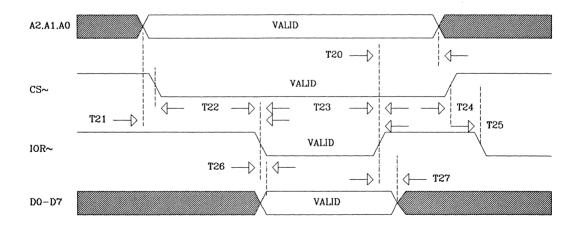

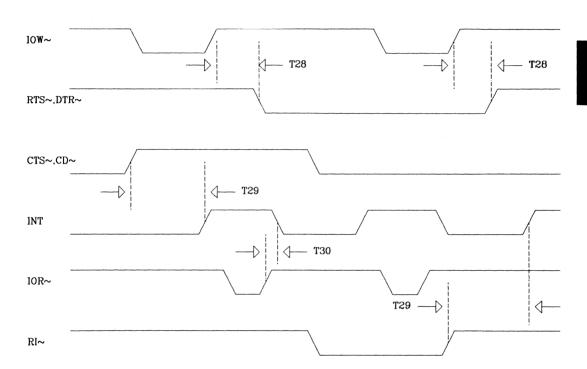

## **TIMING DIAGRAM**

## RECEIVER TIMING

## TRANSMITTER TIMING

4-

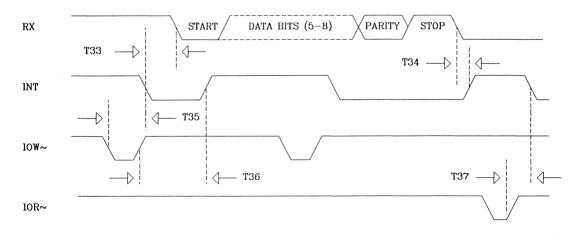

## **TIMING DIAGRAM**

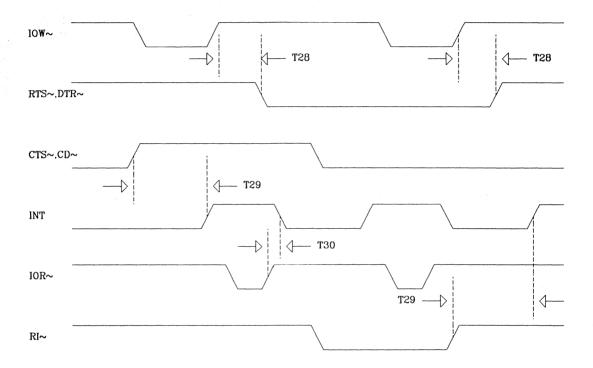

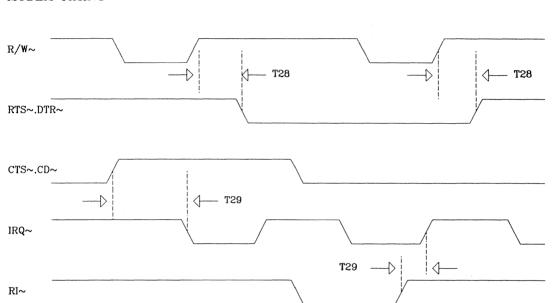

## MODEM TIMING

IOR~

RI~

T29 --->

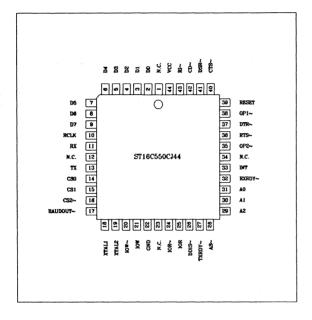

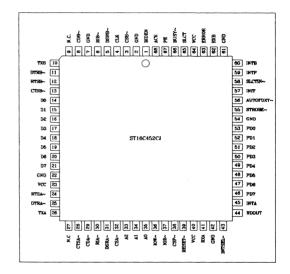

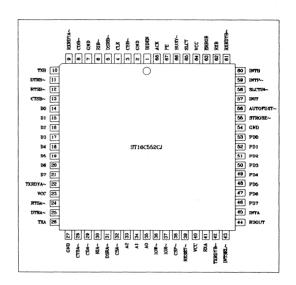

## 44 pin PLCC pinout

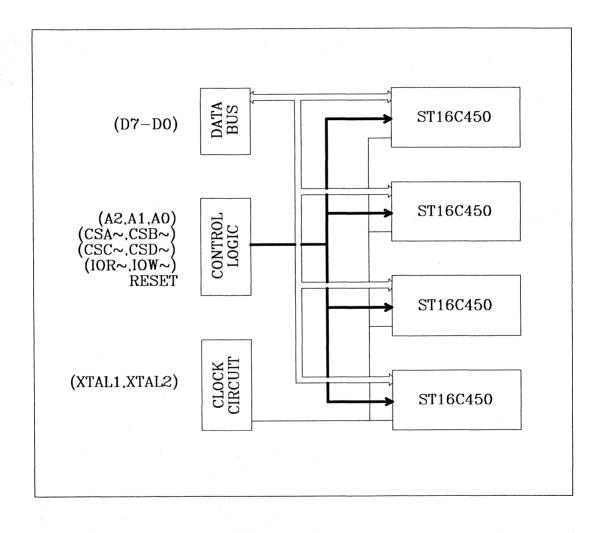

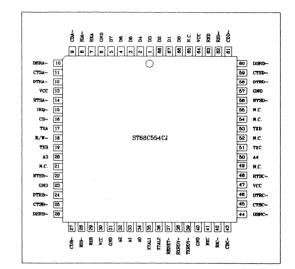

## QUAD ASYNCHRONOUS RECEIVER AND TRANSMITTER

### DESCRIPTION

The ST16C454 is a guad universal asynchronous receiver and transmitter with modem control signals. An internal programmable baud rate generator is provided to select transmit and receive clock rates from 50Hz to 448kHz. The ST16C454 is fabricated in an advanced 1.2 u CMOS process to achieve low drain power and high speed requirements.

### **FEATURES**

- \* Quad ST16C450

- \* Pin-to-pin compatible to ST16C554

- \* Modem control signals (CTS~,RTS~, DSR~, DTR~, RI~, CD~)

- \* Programmable character lengths (5, 6, 7, 8)

- \* Even, odd, or no parity bit generation and detection

- \* Status report register

- \* Independent transmit and receive control

- \* TTL compatible inputs, outputs

### \*\*\*\*\*\*\*\*\*\*\*\* 11 CTSA~ 13 14 15 16 INTA CSA~ TXA INTO CSID~ XXW~ TXB CSB~ INTB IOR~ TXC 18 19 20 21 ST16C454C INTC 22 23 24 25 GND vcc DTVR-DTRC~ CTSB~ CTSC~

### **APPLICATIONS**

- \* Quad serial receiver and/or transmitter

- \* Serial to parallel / parallel to serial converter

- \* Modem handshaking

- \* Fax

- \* Terminals

### ORDERING INFORMATION

Part number ST16C454CJ68 Package **PLCC**

Operating temperature 0° C to +70° C

## **GENERAL DESCRIPTION**

The ST16C454 is an improved, quad version of the NS16450 UART with higher speed operating access time. The ST16C454 performs the parallel to serial/ serial to parallel conversion on the data characters received from the CPU or the MODEM. The on board status registers will provide the error conditions, type and status of the transfer operations being performed. Complete MODEM control capability, and a processor interrupt system that may be software tailored to the user's requirements to minimize the computing required to handle the communications link. The ST16C454 can interface easily to the most popular microprocessors and communications link faults can be detected with internal loopback capability.

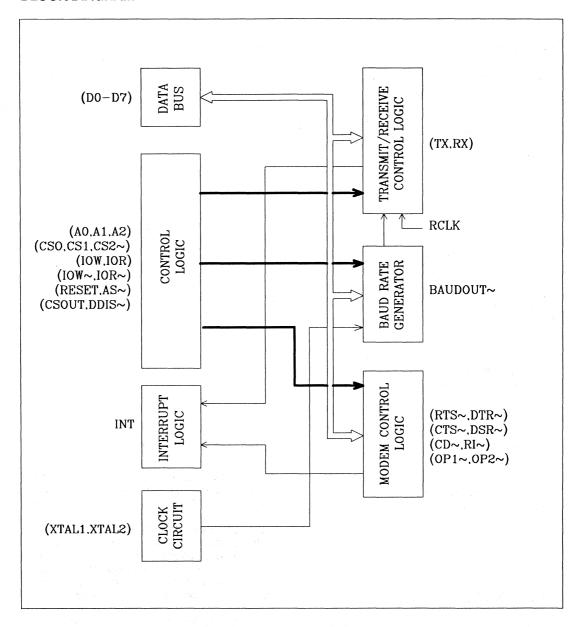

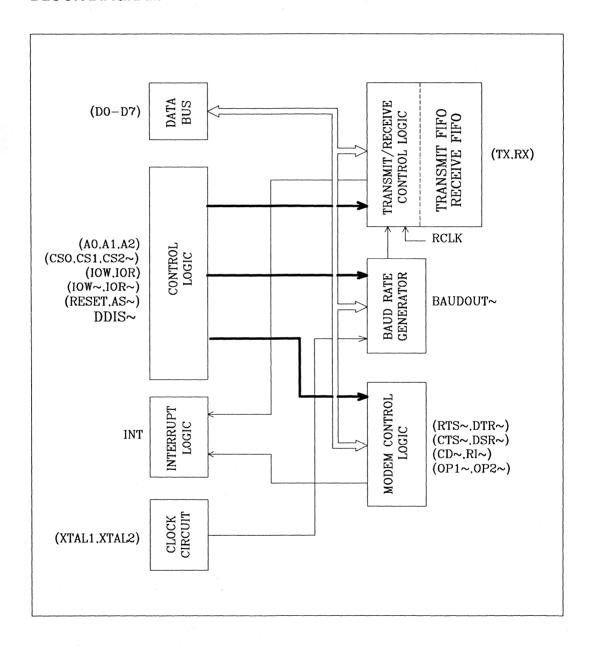

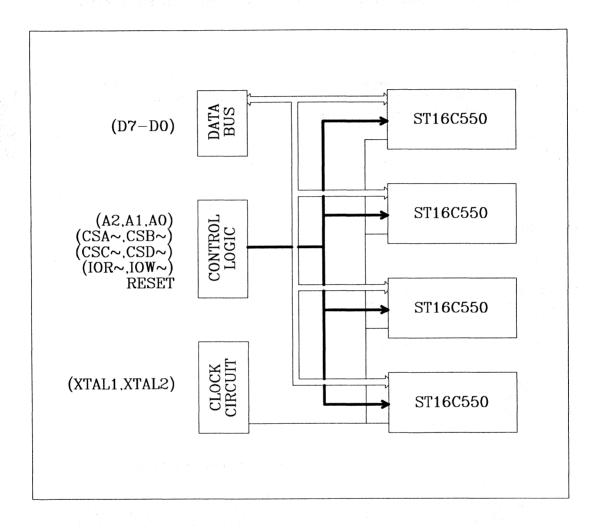

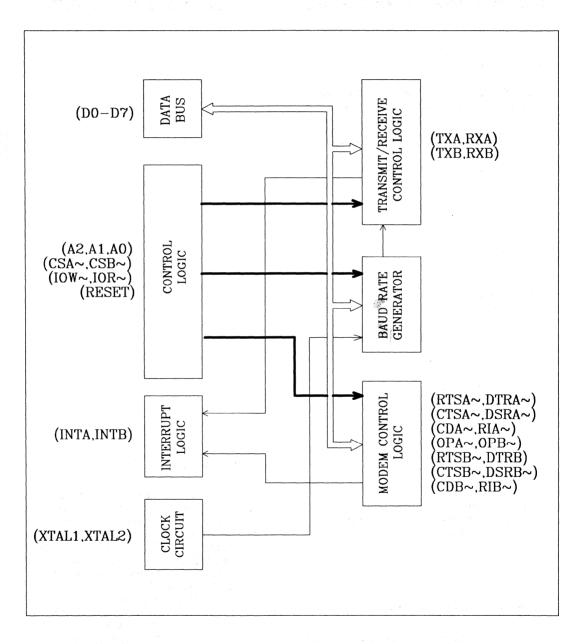

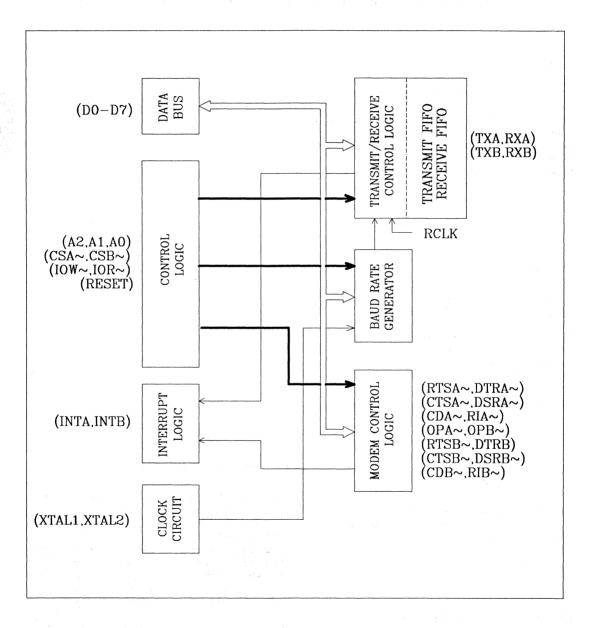

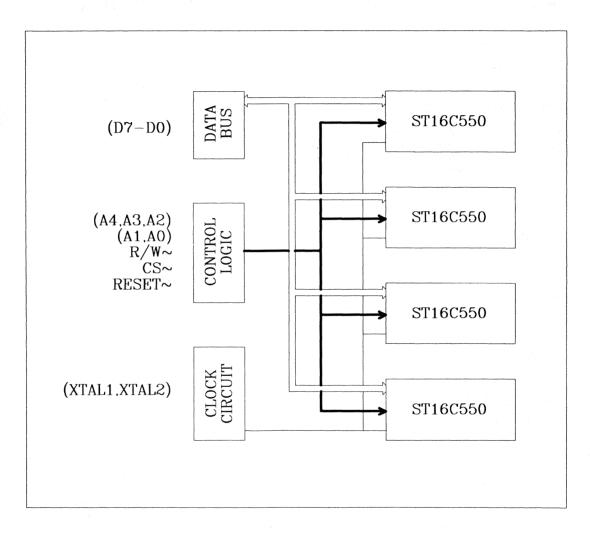

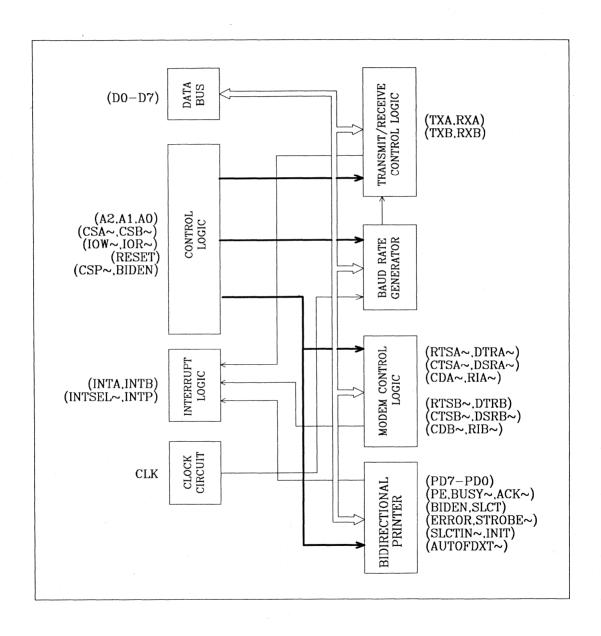

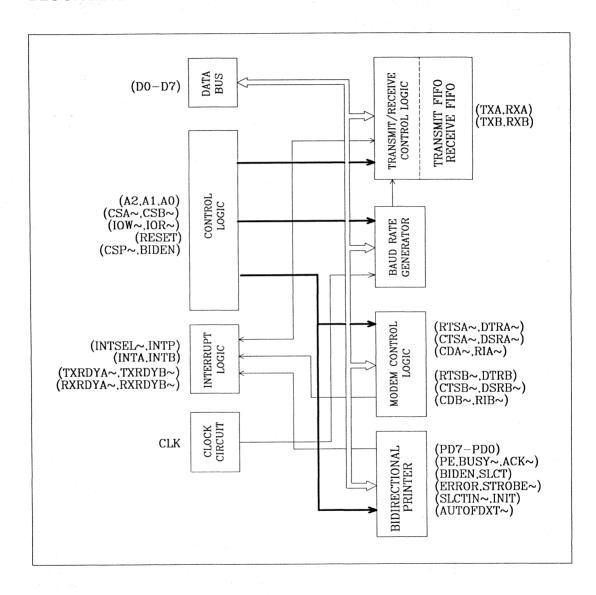

## **BLOCK DIAGRAM**

## **SYMBOL DESCRIPTION**

| Symbol               | Pin            | Signal type  | description                                                                                                                                                                                                                                                                                  |

|----------------------|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D0                | 5-66           | 1/0          | Bidirectional data I/O. Eight bit, three state data bus to transfer information to or from the CPU. D0 is the least significant bit of the data bus and the first serial data bit to be received or transmitted.                                                                             |

| RX A-B<br>RX C-D     | 7,29<br>41,63  | 1            | Serial data input . The serial information received from MODEM or RS232 to ST16C454 receive circuit. A mark (high) is logic one and a space (low) is logic zero. During the local loopback mode the RX input is disabled from external connection and connected to the TX output internally. |

| TX A-B<br>TX C-D     | 17,19<br>51,53 | 0            | Serial data output A. The serial data of channel A is transmitted via this pin with additional start, stop and parity bits. The TX will be held in mark (high) state during reset, local loopback mode or when the transmitter is disabled.                                                  |

| CS A-B~<br>CS C-D~   | 16,20<br>50,54 | , <b>L</b>   | Chip select A-D. (active low) A low at this pin will enable the UART A-D CPU data transfer operation.                                                                                                                                                                                        |

| XTAL1                | 35             | <b>I</b>     | Crystal input 1 or external clock input. A crystal can be connected to this pin and XTAL2 pin to utilize the internal oscillator circuit. An external clock can be used to clock internal circuit and baud rate generator for custom transmission rates.                                     |

| XTAL2                | 36             | l l          | Crystal input 2. See XTAL1.                                                                                                                                                                                                                                                                  |

| IOW~                 | 18             | <b>l</b>     | Write strobe. (active low) A low on this pin will transfer the contents of the CPU data bus to the addressed register.                                                                                                                                                                       |

| CD A-B~<br>CD C-D~   | 9,27<br>43,61  | <br><b>l</b> | Carrier detect A-D. (active low) A low on this pin indicates that carrier has been detected by the modem.                                                                                                                                                                                    |

| GND<br>GND           | 6,23<br>40,57  | 0            | Signal and power ground.                                                                                                                                                                                                                                                                     |

| IOR~                 | 52             | I            | Read strobe. (active low) A low level on this pin will transfer the contents of the ST16C454 data bus to the CPU.                                                                                                                                                                            |

| DSR A-B~<br>DSR C-D~ | 10,26<br>44,60 | 1            | Data set ready A-D. (active low) A low on this pin indicates that MODEM is ready to exchange data with UART.                                                                                                                                                                                 |

| RI A-B~<br>RI C-D~   | 8,28<br>42,62  | l            | Ring detect A-D indicator. (active low) A low on this pin indicates that modem has received a ringing signal from telephone line.                                                                                                                                                            |

## **SYMBOL DESCRIPTION**

| Symbol                 | Pin            | Signal type                                  | Pin description                                                                                                                                                                                                                                                                                                               |

|------------------------|----------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTS A-B~<br>RTS C-D~   | 14,22<br>48,56 | o                                            | Request to send A-D. (active low) To indicate that transmitter has data ready to send. Writing a "1" in the modem control register (MCR bit-1) will set this pin to low state. After the reset this pin will be set to high.                                                                                                  |

| CTS A-B~<br>CTS C-D~   | 11,25<br>45,59 | See J                                        | Clear to send A-D. (active low) The CTS~ signal s a MODEM control function input whose conditions can be tested by reading the MSR BIT-4. CTS~ has no effect on the transmitter output.                                                                                                                                       |

| A2                     | 32             | 1                                            | Address line 2. To select internal registers.                                                                                                                                                                                                                                                                                 |

| A1                     | 33             | 1                                            | Address line 1. To select internal registers.                                                                                                                                                                                                                                                                                 |

| A0                     | 34             | 1                                            | Address line 0. To select internal registers.                                                                                                                                                                                                                                                                                 |

| INT A-B<br>INT C-D     | 15,21<br>49,55 | 0                                            | Interrupt output A-D. (active high) This pin goes high (when enabled by the interrupt enable register) whenever a receiver error, receiver data available, transmitter empty or modem status condition flag is detected on UART A-D.                                                                                          |

| DTR A-B ~<br>DTR C-D ~ | 12,24<br>46,58 | 0                                            | Data terminal ready A-D. (active low) To indicate that ST16C454 is ready to receive data. This pin can be controlled via the modem control register (MCR bit-0). Writing a "1" at the MCR bit-0 will set the DTR ~ output to low. This pin will be set to high state after writing a "0" to that register or after the reset. |

| RESET                  | 37             | ı                                            | Master reset. (active high) A high on this pin will reset all the outputs and internal registers. The transmitter output and the receiver input will be disabled during reset time.                                                                                                                                           |

| vcc                    | 13,30<br>47,64 | 1                                            | Power supply input.                                                                                                                                                                                                                                                                                                           |

|                        | 3<br>2 - 2     |                                              |                                                                                                                                                                                                                                                                                                                               |

|                        | 7.4%.          |                                              |                                                                                                                                                                                                                                                                                                                               |

|                        |                | e de Lejaro († 184)<br>Lejaro Lejaro († 184) |                                                                                                                                                                                                                                                                                                                               |

### PROGRAMMING TABLE

| DLAB | A2 | A1 | A0 | READ MODE                 | WRITE MODE                |

|------|----|----|----|---------------------------|---------------------------|

| 0    | 0  | 0  | 0  | Receive Holding Register  | Transmit Holding Register |

| 0    | 0  | 0  | 1  | ů ů                       | Interrupt Enable Register |

| X    | 0  | 1  | 0  | Interrupt Status Register |                           |

| X    | 0  | 1  | 1  |                           | Line Control Register     |

| X    | 1  | 0  | 0  |                           | Modem Control Register    |

| X    | 1  | 0  | 1  | Line Status Register      | <b>G</b>                  |

| x    | 1  | 1  | 0  | Modem Status Register     |                           |

| X    | 1  | 1  | 1  | Scratchpad Register       | Scratchpad Register       |

| 1    | 0  | 0  | 0  |                           | LSB of Divisor Latch      |

| 1    | 0  | 0  | 1  |                           | MSB of Divisor Latch      |

|      | 1  | 1  |    |                           |                           |

### REGISTER FUNCTIONAL DESCRIPTIONS

## TRANSMIT AND RECEIVE HOLDING REGISTER A-D

The serial transmitter section consists of a Transmit Hold Register A-D and Transmit Shift Register A-D. The status of the transmit hold register is provided in the Line Status Register A-D. Writing to this register will transfer the contents of the data bus (D7-D0) to the transmit holding register A-D whenever the transmitter holding register A-D or transmitter shift register A-D is empty. The transmit holding register empty A-D flag will be set to "1" when the transmitter is empty or data is transferred to the transmit shift register A-D. Note that a write operation should be performed when the transmit holding register empty flag is set.

On the falling edge of the start bit, the receiver internal counter will start to count 7 1/2 clocks (16x clock) which is the center of the start bit. The start bit is valid if the RX A-D is still low at the mid-bit sample of the start bit. Verifying the start bit prevents the receiver from assembling a false data character due to a low going noise spike on the RX A-D input. Receiver status codes will be posted in the Line Status Register A-D.

### PROGRAMMABLE BAUD RATE GENERATOR

The ST16C454 contains a programmable Baud Rate Generator that is capable of taking any clock input from DC-16 MHz and dividing it by any divisor from 2 to 2 16 -1. Customize Baud Rates can be achieved by selecting proper divisor values for MSB and LSB of baud rate generator.

## INTERRUPT ENABLE REGISTER A-D

The Interrupt Enable Register A-D masks the incoming interrupts from receiver ready, transmitter empty, line status and modem status registers to the INT A-D output pin.

### IER BIT-0:

0 = disable the receiver ready interrupt 1 = enable the receiver ready interrupt

### IER BIT-1:

0 = disable transmitter empty interrupt 1 = enable transmitter empty interrupt

#### IER BIT-2:

0 = disable receiver line status interrupt 1 = enable receiver line status interrupt

#### IER BIT-3:

0 = disable the modem status register interrupt 1 = enable the modem status register interrupt

### **IER BIT 7-4:**

All these bits are set to logic zero.

### **INTERRUPT STATUS REGISTER A-D**

The ST16C454 provides four level prioritized interrupt conditions to minimize software overhead during data character transfers. The Interrupt Status Register A-D provides the source of the interrupt in prioritized manner. During the read cycle, the ST16C454 provides the highest interrupt level to be serviced by the CPU. No other interrupts are acknowledged until the particular interrupt has been serviced. The following are the prioritized interrupt levels:

| Pri | iorit | y le | vel | Source of the interrupts                       |

|-----|-------|------|-----|------------------------------------------------|

| Р   | D2    | D1   | D0  |                                                |

| 1   | 0     | 0    | 0   | LSR A-D (Receiver Line Status<br>Register)     |

| 2   | 0     | 0    | 0   | RXRDY A-D (Received Data<br>Ready)             |

| 3   | 0     | 0    | 0   | TXRDY A-D (Transmitter holding register empty) |

| 4   | 0     | 0    | 0 , | MSR A-D (Modem Status Register)                |

### ISR BIT-0:

0 = an interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt service routine

1 = no interrupt pending

### **ISR BIT 1-2:**

Logical combination of these bits, provides the highest priority interrupt pending.

### **ISR BIT 3-7:**

These bits are not used and are set to zero.

### LINE CONTROL REGISTER A-D

The Line Control Register is used to specify the asynchronous data communication format. The number of the word length, stop bits, and parity can be selected by writing appropriate bits in this register.

### LCR BIT1-0:

These two bits specify the word length to be transmitted or received.

00=5 bits word length

01 = 6 bits word length

10=7 bits word length

11 = 8 bits word length

### LCR BIT-2:

The number of stop bits can be specified by this bit. 0=1 stop bit, when word length=5, 6, 7, 8 bits 1=1 and 1/2 stop bit, when word length=5 bits

1=2 stop bits, word length=6, 7, 8 bits

### 1=2 stop bits, word length=6, 7, 6 bits

#### LCR BIT-3:

Parity or no parity can be selected via this bit. 0 = no parity

1 = a parity bit is generated during the transmission; receiver also checks for received parity

### LCR BIT-4:

If the parity bit is enabled, LCR BIT-4 selects the even or odd parity format.

0 = odd parity is generated by calculating odd number of 1's in the transmitted data; receiver also checks for same format.

1 = an even parity bit is generated by calculating the number of even 1's in the transmitted data; receiver also checks for same format.

### LCR BIT-5:

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5=1 and LCR BIT-4=0, parity bit is forced to "1" in the transmitted and received data.

LCR BIT-5 = 1 and LCR BIT-4 = 1, parity bit is forced to "0" in the transmitted and received data.

### LCR BIT-6:

Break control bit.

1 = forces the transmitter output (TX A-D) to go low to alert the communication terminal

0 = normal operating condition

### LCR BIT-7:

The internal baud rate counter latch enable (DLAB). 0=normal operation

1 = select divisor latch register

### MODEM CONTROL REGISTER A-D

This register controls the interface with the MODEM or a peripheral device (RS232).

### MCR BIT-0:

0=force DTR~ output to high 1=force DTR~ output to low

### MCR BIT-1:

0=force RTS~ output to high 1=force RTS~ output to low

### MCR BIT-2:

x=not used

### MCR BIT -3:

0 = Disable the INT output 1 = Enable the INT output

### MCR BIT -4:

0 = normal operating mode

1 = enable local loop-back mode (diagnostics). The transmitter output (TX A-D) is set high (Mark condition), the Receiver inputs (RX A-D , CTS A-D  $\sim$ , DSR A-D  $\sim$ , CD A-D  $\sim$ , and RI A-D  $\sim$ ) are disabled. Internally, the transmitter output is connected to the receiver input and DTR A-D  $\sim$ , RTS A-D  $\sim$  and OP A-D  $\sim$  are connected to modem control inputs. In this mode , the receiver and transmitter interrupts are fully operational. The Modem Control Interrupts are also operational, but the interrupt sources are now the lower four bits of the Modem Control Register instead of the four Modem Control Inputs. The interrupts are still controlled by the IER A-D.

### MCR BIT 5-7:

Not used. Are set to zero permanently.

### LINE STATUS REGISTER A-D

This register provides the status of data transfer to CPU.

### LSR BIT-0:

0=no data in receive holding register 1=a data has been received and saved in the receive holding register

### LSR BIT-1:

0 = no overrun error (normal)

1 = overrun error, next character arrived before receive holding register was empty

### LSR BIT-2:

0 = no parity error (normal)

1 = parity error, received data does not have correct parity information

### LSR BIT-3:

0 = no framing error (normal)

$1\!=\!\text{framing}$  error received, received data did not have a valid stop bit

#### LSR BIT-4:

0 = no break condition (normal)

1 = receiver received a break signal (RX was low for one character time frame)

### LSR BIT-5:

0 = transmit holding register is full; ST16C454 will not accept any data for transmission

1 = transmit holding register is empty; CPU can load the next character

### LSR BIT-6:

0=transmitter holding and shift registers are full 1=transmitter holding and shift registers are empty

### LSR BIT-7:

This bit is not used and is set to zero.

### MODEM STATUS REGISTER A-D

This register provides the current state of the control lines from the modem or peripheral to the CPU. Four bits of this register are used to indicate the changed information. These bits are set to "1" whenever a control input from the MODEM changes state. They are set to "0" whenever the CPU reads this register.

### MSR BIT-0:

Indicates that the CTS~ input to the ST16C454 has changed state since the last time it was read.

### MSR BIT-1: